1. Tujuan

- Dapat mengetahui apa itu DC Bias With Voltage Feedback.

- Dapat mempelajari teori dari DC Bias With Voltage Feedback.

- Dapat memahami prinsip kerja rangkaian DC Bias With Voltage Feedback.

2. Komponen

- Baterai, berfungsi sebagai sumber arus listrik.

- DC Voltmeter, berfungsi untuk mengetahui beda potensial tegangan DC antara 2 titik pada suatu beban listrik atau rangkaian elektronika.

- DC Ammeter, berfungsi untuk mengetahui arus tegangan DC pada suatu rangkaian listrik atau suatu beban listrik.

Resistor 1k Ohm

Resistor berfungsi untuk menghambat arus dalam rangkaian listrik. Cara menghitung nilai resistansi resistor dengan gelang warna :

1. Masukan angka langsung dari kode warna gelang pertama.

2. Masukan angka langsung dari kode warna gelang kedua.

3. Masukan angka langsung dari kode warna gelang ketiga.

4. Masukkan jumlah nol dari kode warna gelang ke-4 atau pangkatkan angka tersebut dengan 10 (10^n), ini merupakan nilai toleransi dari resistor.

3. Dasar Teori

- Self-Bias Configuration

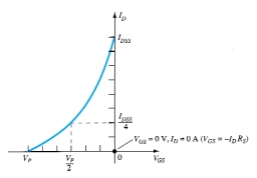

Dengan konfigurasi self-bias, 2 supply DC tidak dibutuhkan. Kendali gerbang ke sumber tegangan ditentukan oleh tegangan yang melintasi resistor RS yang diperkenalkan pada kaki sumber dari konfigurasi seperti yang ditunjukkan pada Gambar. 6.8.

Gambar 6.8 Self-Bias Configuration

Untuk analisis DC, kapasitor kembali dapat diganti dengan rangkaian terbuka dan resistor RG diganti dengan ekuivalen hubung singkat karena IG = 0 A. Hasilnya adalah rangkaian pada Gambar 6.9 untuk analisis DC.

Gambar 6.99 Analisis dc pada Self-Bias Configuration

Arus melalui yang memlui RS adalah arus sumber IS, dimana IS=ID

Untuk loop tertutup yang ditunjukkan pada Gambar 6.9, ditemukan bahwa

Persamaan (6.10) ditentukan oleh konfigurasi jaringan, dan persamaan Shockley mengaitkan jumlah input dan output perangkat. Kedua persamaan berhubungan dengan dua variabel yang sama, yang memungkinkan solusi matematika atau grafis. Solusi matematika dapat diperoleh mensubstitusikan Persamaan. (6.10) ke dalam persamaan Shockley dan menghasilkan :

Hasil di atas memperlihatkan solusi matematika. Untuk menentukan solusi grafis, terlebih dahulu harus ditetapkan karakteristik transfer perangkat seperti yang ditunjukkan pada Gambar 6.10. Karena Persamaan. (6.10) menghasilkan garis lurus pada grafik yang sama, lalu mengidentifikasi dua titik pada grafik yang ada di garis dan menggambar garis lurus antara dua titik. Kondisi yang paling jelas untuk diterapkan adalah ID = 0 A karena menghasilkan VGS = - IDRS = (0 A) RS = 0 V. Untuk Persamaan. (6.10), satu titik pada garis lurus didefinisikan oleh ID = 0 A dan VGS = 0 V, seperti yang tampak pada Gambar 6.10.

Gambar 6.10 Menentukan Titik pada Garis Self-Bias

Titik kedua pada Persamaan. (6.10) membutuhkan VGS atau ID dan tingkat yang sesuai dari kuantitas lainnya ditentukan menggunakan Persamaan. (6.10). Level ID dan VGS yang dihasilkan kemudian akan menentukan titik lain pada garis lurus dan memungkinkan gambar garis lurus yang sebenarnya. Misalkan, kita memilih level ID yang sama dengan setengah tingkat kejenuhan yaitu :

Hasilnya adalah titik kedua untuk plot garis lurus seperti yang ditunjukkan pada Gambar 6.11. Garis lurus seperti yang didefinisikan oleh Persamaan. (6.10) kemudian ditarik dan titik diam diperoleh pada persimpangan plot garis lurus dan kurva karakteristik perangkat. Nilai diam ID dan VGS kemudian dapat ditentukan dan digunakan untuk menemukan angka lainnya.

Gambar 6.11 Garis Self-Bias

VDS dapat ditentukan dengan menerapkan hukum KVL ke rangkaian output, dengan hasil :

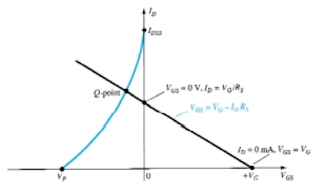

- Voltage-Divider Biasing

Pengaturan bias pembagi tegangan yang diterapkan pada amplifier transistor BJT juga diterapkan pada amplifier FET seperti yang ditunjukkan oleh Gambar. 6.20. Konstruksi dasarnya benar-benar sama, tetapi analisis dc masing-masing sangat berbeda. IG 0 A untuk FET am plifiers, tetapi besarnya IB untuk penguat BJT umum-emitor dapat mempengaruhi dc tingkat arus dan tegangan di sirkuit input dan output. Ingat bahwa IB menyediakan hubungan antara sirkuit input dan output untuk konfigurasi pembagi tegangan BJT sementara VGS akan melakukan hal yang sama untuk konfigurasi FET.

Gambar 6.20 Voltage-Devider Bias

Gambar 6.21 Analisis DC untuk Rangkaian 6.20

Rangkaian Gambar 6.20 digambar ulang seperti yang ditunjukkan pada Gambar. 6.21 untuk analisis dc. Perhatikan bahwa semua kapasitor, termasuk CS kapasitor bypass, telah diganti oleh setara "sirkuit terbuka". Selain itu, sumber VDD dipisahkan menjadi dua sumber yang sama untuk memungkinkan pemisahan lebih lanjut dari daerah input dan output dari pekerjaan bersih. Sejak IG 0 A, hukum Kirchhoff saat ini mensyaratkan bahwa IR1 IR2 dan seri sirkuit ekivalen yang muncul di sebelah kiri gambar dapat digunakan untuk menemukan level VG. Tegangan VG, sama dengan tegangan pada R2, dapat ditemukan menggunakan aturan pembagi tegangan sebagai berikut:

Dengan menerapkan hukum tegangan Kirchhoff searah jarum jam ke arah yang ditunjukkan dari Gambar. 6.21 akan menghasilkan

Hasilnya adalah persamaan yang terus menyertakan dua variabel yang sama yang muncul dalam persamaan Shockley: VGS dan ID. Besaran VG dan RS ditetapkan oleh garis lurus. Persamaan (6.16) tetap persamaan untuk garis lurus, tetapi asal tidak lagi menjadi titik dalam plot garis. Prosedur untuk membuat plot Persamaan. (6.16) tidak sulit dan akan dilanjutkan sebagai berikut. Karena garis lurus pun membutuhkan dua titik untuk didefinisikan, mari kita gunakan fakta bahwa di mana saja pada sumbu horizontal Gambar 6.22 arus ID = 0 mA. Oleh karena itu, jika memilih ID=0 mA, kami pada dasarnya menyatakan bahwa kami berada di suatu tempat pada sumbu horizontal. Lokasi yang tepat dapat ditentukan hanya dengan mengganti ID = 0 mA ke Persamaan. (6.16) dan menemukan nilai yang dihasilkan dari VGS sebagai berikut:

Hasilnya menentukan bahwa setiap kali kita merencanakan Persamaan. (6.16), jika kita memilih ID 0 mA, the nilai VGS untuk plot adalah VG volts. Titik yang baru saja ditentukan muncul pada Gambar. 6.22.

Gambar 6.22 Grafik Persamaan Voltage-Devider Configuration

Untuk titik lain, mari kita gunakan fakta bahwa pada titik mana pun pada vertikal Sumbu VGS=0V dan pecahkan untuk nilai ID yang dihasilkan:

4. Prinsip Kerja Rangkaian

Self-bias configuration menghilangkan kebutuhan dua persediaan dc. Tegangan gate-to-source pengendali sekarang ditentukan oleh tegangan pada resistor RS yang diperkenalkan di kaki sumber konfigurasi. Untuk analisis dc, kapasitor dapat kembali digantikan oleh "sirkuit terbuka" dan resistor RG diganti dengan ekuivalen rangkaian pendek sejak IG = 0 A.

Tegangan VG didapatkan dari tegangan di R2 dari hubungan VDD seri dengan R1 dan R2. Sejak IG 0 A, hukum KCL saat ini mensyaratkan bahwa IR1=IR2 dan rangkaian seri ekivalen digunakan untuk menemukan tegangan VG. Tegangan VG, sama dengan tegangan yang melewati R2,

5. Gambar Rangkaian

6. Video

7. Link Download

Download Datasheet NJEFT silahkan klik di sini

Download HTML silahkan klik di sini

Download Bentuk Rangkaian 6.8 silahkan klik di sini

Download Bentuk Rangkaian 6.9 silahkan klik di sini

Download Bentuk Rangkaian 6.20 silahkan klik di sini

Download Bentuk Rangkaian 6.21 silahkan klik di sini

Download Video Simulasi Rangkaian 6.8 silahkan klik di sini

Download Video Simulasi Rangkaian 6.9 silahkan klik di sini

Download Video Simulasi Rangkaian 6.20 silahkan klik di sini

Download Video Simulasi Rangkaian 6.21 silahkan klik di sini

Download Video datasheet resistor silahkan klik di sini

Download Video datasheet capacitor silahkan klik di sini

Tidak ada komentar:

Posting Komentar